# SIZING OF A STAND-ALONE PEM FUEL CELL POWER SYSTEM PART III: DESIGN OF THE PUSH-PULL CONVERTER AND THE SINGLE-PHASE INVERTER

## MARIAN GAICEANU

"Dunarea de Jos" University of Galati,

**Abstract:** The third part of the paper concludes the design tool of a stand-alone power system based on a proton exchange membrane (PEM) fuel cell stack by means of Microsoft Excel. The design of the push-pull converter, single-phase inverter and of the output filter are described in separate sections of the paper. All the data are derived from the specific load conditions for the stationary application. The design tool is used in order to choose an adequate topology for the PEM fuel cell power system.

**Keywords:** Stand-alone, PEM fuel cell, power system, design, push-pull converter, single-phase inverter, output filter

## 1. INTRODUCTION

This paper deals with introducing of the PEM fuel cells by means of a power converters. The configuration results by using a push-pull dc-dc converter at the fuel cell side followed by a full-bridge PWM inverter and a low-pass filter at the output side [1],[2]. In this paper, a design for push-pull converter and a power inverter is presented for conversion of DC power from fuel cells to single phase AC power. During the start-up and for the dc loads purpose a half-bridge dc-dc converter delivers the required energy from the battery with the adequate parameters, being compatible with the aforementioned configuration [3].

## 2. PUSH-PULL TECHNICAL SPECIFICATIONS AND DESIGN

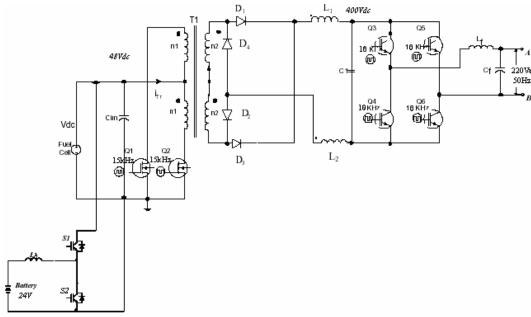

Figure 1 shows the topology of the fuel cell inverter system which comprises a DC-DC boost circuit, a DC-AC inverter circuit and an output filter. The battery banks are connected to DC bus through a half bridge DC-DC converter[3]. The DC input from the fuel cell (48 VDC nominal) is first converted to a regulated 400 VDC using a high frequency push-pull DC-DC converter. The DC-DC conversion stage consists of a high-frequency transformer.

Isolation is provided for safety and system protection. The 400V DC-DC converter output is converted to 220V, 50Hz, single-phase AC by means of a PWM driven inverter stage. To obtain single phase output, a full-bridge inverter is used. An output LC filter stage is employed to produce a low THD AC waveform. Low loss, high switching frequency MOSFET and IGBT switches have been employed to achieve a higher efficiency, lower size and volume of the fuel cell inverter system [4]-[7].

## 2.1 Push-pull converter design

Fig.1 Circuit diagram of the PEM fuel cell power system for stand alone application

Table 1. Push-pull converter design

|    | Design specific                     | ations   |    |

|----|-------------------------------------|----------|----|

| 1  | Nominal input voltage               | 48.00    | V  |

| 2  | Minimum input voltage               | 42.00    | V  |

| 3  | Maximum input voltage               | 52.00    | V  |

| 4  | Output voltage                      | 400.00   | V  |

| 5  | Output current                      | 26.02    | Α  |

| 6  | Frequency                           | 15000.00 | Hz |

| 7  | Pout push pull[W]                   | 10407.73 | W  |

| 8  | Diode voltage drop                  | 1.00     | V  |

| 9  | Duty ratio max                      | 0.47     |    |

| 10 | Output power of the FC power system | 10095.50 |    |

| 11 | Inverter Efficiency                 | 0.97     |    |

| 12 | DC-DC conv Efficiency               | 0.97     |    |

In this section design of the push-pull DC-DC converter is detailed [8]. The push-pull converter belongs to the feedforward converter family[9]. Figure 1 shows the circuit diagram of the push-pull DC/DC converter. Fuel cell output is connected to the DC/DC converter as shown. With reference to Fig. 1, Q1 and Q2 are turned on and off alternately at a switching frequency of 15kHz and accordingly the current flows through the respective winding of the transformer. When Q1switches ON, D1 and D3 conduct. Similarly, when Q2 switches ON, D2 and D4 conduct. The components L1, L2 and C1 form a LC filter network.

The considered power output  $P_0$  of the inverter is 10000W. Assuming an efficiency of 95% for the inverter and the DC-DC converter, the input power,  $P_{in}$ , is calculated according to:

Table 2. Push-pull converter switch ratings

| Output data                                                       |       |   |  |  |

|-------------------------------------------------------------------|-------|---|--|--|

| Input power (Pin)                                                 | 11050 | W |  |  |

| Input current, Iin[A]                                             | 263   | Α |  |  |

| The rating current of the switches, IT1=I <sub>Mosfet,1</sub> [A] | 180.3 | A |  |  |

$$P_{in} = \frac{P_0}{\eta_{inv} \cdot \eta_{dc}} = 11050W \tag{1}$$

A nominal fuel cell input voltage,  $V_{in}$ = 48VDC, is assumed. The output voltage of the dc-dc converter is  $V_{o}$ = 400VDC.

Designing for the low input line condition (Vin,min=42VDC), input current Iin,max from the fuel cell is,

$$I_{in}^{\text{max}} = \frac{P_{in}}{V_{in}^{\text{min}}} = \frac{11050W}{42A} = 263A \tag{2}$$

At the maximum duty ratio of 0.47, rms current rating IT=I<sub>Mosfet,1</sub> of the switches are equals,

$$I_{Mosfet,1} = I_{in} \sqrt{D_{\text{max}}} = 263\sqrt{0.47} = 180.3A$$

(3)

IRFP260N (200V, 50A) MOSFETs with 4 devices in parallel in each leg are chosen.

## 2.1.1 High frequency transformer

Center taps are available on both the primary and secondary sides as shown in Figure 1. The VA rating of the transformer is defined as the sum of the total primary and secondary winding VA divided by two,

$$S_T = \frac{1}{2} (S_1 + S_2) \tag{4}$$

$$S_1 = 2 \frac{V_{in}}{\sqrt{2}} \cdot \frac{I_{in}}{\sqrt{2}}, \ S_2 = 2V_{N2}I_{N2}, \ \ (5)$$

Voltage ratings of the transformer are selected as:

- primary voltage=80V,  $V_{primary} = 2V_{N1}$ ,  $V_{primary} = 80V$

- secondary voltage=400V,  $V_{\text{sec}} = 400V$

Table 3. High frequency transformer sizing

| High frequency transformer-center taps |                  |          |                      |  |  |

|----------------------------------------|------------------|----------|----------------------|--|--|

|                                        | VN1[V]<br>VN2[V] |          | 42.00                |  |  |

| Input data                             |                  |          | 200.00               |  |  |

|                                        | IN1=Iin[A]       |          | 263                  |  |  |

|                                        | Vin1[V]          | 84.00    | Primary voltage      |  |  |

|                                        | Vout[V]          | 400.00   | Secondary<br>voltage |  |  |

|                                        | Kt               | 4.76=>   | Kt=5                 |  |  |

| Output data                            | IN2[A]           | 51.09    |                      |  |  |

|                                        | S1[VA]           | 10729.62 | S2-check             |  |  |

|                                        | S2[VA]           | 20437.37 | 21459.24             |  |  |

|                                        |                  | 15583.50 | VA rating of the     |  |  |

|                                        | Stotal[VA]       | 16000.00 | transformer          |  |  |

For obtaining an output voltage of 400VDC for the push-pull converter, a turns ratio of K=5 is selected for the transformer.

$$\frac{V_{\text{sec}}}{V_{prim}} = K \tag{6}$$

## 2.1.2 Diode ratings

The reverse blocking voltage is equal to the DC link voltage 400V. Since each diode is clamped to the mid-point of the DC-link (200V), each diode can be rated for 300V. The rms current through the diode, ID, is given by

Table 4. Diode ratings

| DIODE           |                              |        |              |       |                                       |

|-----------------|------------------------------|--------|--------------|-------|---------------------------------------|

| Voltage Voltage | Reversal blocking voltage[V] | 400.00 |              |       | 60EPU04                               |

| J               | VD1=VD2[V]                   | 200.00 | VD1final>VD1 | 300 V | 400V,<br>60A)                         |

| Current         | ID1rms[A]                    | 37.3   |              |       | , , , , , , , , , , , , , , , , , , , |

$I_D = \frac{I_{in}}{K\sqrt{2}} = 37.3A$  (7)

The 60EPU04 (400V, 60A) fast recovery diodes are selected.

## 2.1.3 Coupled Inductor design for DC-DC stage

The inductor acts as a current link between two voltage sources (the input and the DC capacitor). The RMS output current I<sub>o</sub>,

Table 5. Output inductor design

| Output inductor design (to prevent the transformer saturation) |         |  |

|----------------------------------------------------------------|---------|--|

| The output current, Io[A]                                      | 25.24   |  |

| The RMS ripple of Io [%]                                       | 0.15    |  |

| The peak-to-peak ripple[A]                                     | 8.00    |  |

| Voltage drops to the secondary side[V]                         | 10.00   |  |

| The secondary voltage, Vsec[V]                                 | 410.00  |  |

| Time correspond to the max duty cycle [us]                     | 31.33   |  |

| The slope of the inductor current [A/us]                       | 0.26    |  |

| The required value of the inductor [uH]                        | 1605.83 |  |

$$I_0 = \frac{P_0}{V_{dc}} = \frac{10500}{400} = 26A \tag{8}$$

Assuming the RMS ripple of Io to be 15%,

$$\Delta I_0 = 0.15 I_0 \tag{9}$$

the peak-to-peak ripple is 8A:

$$\Delta I_0^{pp} = \Delta I_0 \cdot 2 \tag{10}$$

Taking into consideration the voltage drops to the secondary side,  $\Delta V_{\rm sec} = 10V$ , the secondary voltage becomes:

$$V_0 = V_{\text{sec}} + \Delta V_{\text{sec}} = 400 + 10 = 410V \tag{11}$$

Thus the required value of inductor can be computed as

$$L = V_0 \frac{dt}{dI} = 410 \frac{31.33 \,\mu s}{8A} = 1606 \,\mu H \tag{12}$$

where d*I*-the peak to peak current ripple

The slope of the inductor current

$$s = \frac{dI}{dt} = \frac{8A}{31.33\,\mu s} = 0.26 \left(\frac{A}{\mu s}\right)$$

(13)

Time correspond to the max duty cycle [µs]

$$dt = \frac{D_{\text{max}}}{f_{sw}} = \frac{0.47}{15000} = 31.33 \,\mu\text{s} \tag{14}$$

## 3. SINGLE-PHASE INVERTER DESIGN

The inverter system consists of one full-bridge inverters, utilizing dc link capacitors followed by output filters.

Table 6. Inverter specifications

| Single-phase Inverter Design |                                  |          |          |  |  |

|------------------------------|----------------------------------|----------|----------|--|--|

|                              | At full load the VA output power | S[VA]    | 11877.06 |  |  |

| Input Data                   | The modulation index             | ma       | 0.90     |  |  |

|                              | The fundamental output frequency | f1[Hz]   | 50.00    |  |  |

|                              | The rms phase loadcurrent        | IArms[A] | 53.99    |  |  |

|                              | The switching frequency, fsw[Hz] | fsw[Hz]  | 10000.00 |  |  |

The front-end DC-DC converter maintains equal 400V on the dc-link capacitors, and the inverter operates to generate a single-phase 220Vac, 50Hz output in stand-alone mode[9].

In this section the ratings of the power components of the inverter system are calculated.

A detailed list of the inverter requirement for the inverter design is [9],

- Continuous power, displacement factor 0.85 leading or lagging, 10kW overload for 1 min

- Output voltage: 220V.

- Output frequency: 50Hz±0.1Hz.

- Output voltage THD : less than 5% when supplying a stand nonlinear test load.

- Output voltage regulation quality : output voltage tolerance no wider than  $\pm 6\%$ .

## 3.1 DC Link Capacitor Design

Taking into consideration the worst case, i.e. 10KW output load of the FC system for 1 minute at displacement factor  $\cos \varphi = 0.85$ , the output VA becomes:

$$VA_{out} = \frac{10000}{0.85} = 11877VA \tag{15}$$

Table 7. DC link capacitor design

| The DC link capacitor |                                                        |           |          |  |

|-----------------------|--------------------------------------------------------|-----------|----------|--|

|                       | The fundamental harmonic component of the load current | I1[A]     | 44.25    |  |

| Input data            | The third harmonic component:                          | I3[A]     | 30.98    |  |

|                       | The largest component of the DC link capacitor         | Imax[A]   | 44.25    |  |

|                       | The rms value of the capacitor current                 | ic,rms[A] | 44.25    |  |

| Output                | The voltage ripple limit[%]                            |           | 0.05     |  |

| Output<br>data        | The voltage ripple value                               | ΔVc[V]    | 20.00    |  |

| uata                  | The pulsation[rad/s]                                   | omega     | 314.00   |  |

|                       | The DC link capacitor [uF]                             | C1        | 12811.62 |  |

The full load current of each phase is given by,

$$I_{a,rms} = \frac{11877VA}{220V} = 54A \quad (16)$$

For the sake of simplicity, the output current  $i_a$  is assumed to consist of only fundamental (Ia, I) and third harmonic (Ia, 3). Further, assuming Ia, 3 = 0.7Ia, I since this is a typical case of a single phase rectifier type nonlinear load,

$$I_{a,rms} \cong \sqrt{I_{a,1}^2 + I_{a,3}^2} = 1,22I_{a,1}$$

(17)

Therefore, the fundamental rms value of each phase output current becomes,

$$I_{a,1} = \frac{I_{a,rms}}{1.22} \Rightarrow I_{a,1} = 44.21A$$

(18)

For a permissible voltage ripple  $\Delta V_{c1}$  less than 10% or 10V, capacitance can be obtained by,

$$C_1 = \frac{I_{a,1}}{\omega \Delta V_{c1}} = \frac{44,21}{2\pi 50 \cdot 20} = 12811,62 \,\mu F \tag{19}$$

The peak voltage rating of the dc link capacitor C<sub>1</sub> becomes,

$$V_{c1,peak} = V_{DC} + \Delta V_{c.1} = 420V \tag{20}$$

Based on these designed values, an actual device of 500V-13mF was selected from a manufacture.

## 3.2 Inverter switches

The peak voltage rating of each IGBT is 420V which is the peak dc link voltage.

Based on these designed values, IGBTs with 600V-48A rating were selected from a manufacture:

Table 8. Sizing of the inverter power switch

| Inverter switch ratings |                               |        |       |  |

|-------------------------|-------------------------------|--------|-------|--|

| Input data              | The rms current               | isA[A] | 19.48 |  |

| input data              | The rms switch current rating | IT[A}  | 13.77 |  |

## 4. LC OUTPUT INTERFACE DESIGN

To satisfy THD requirement of less than 5% and to limit the ripple voltage across the filter capacitor generated from the third harmonic load current

The filter components (inductance and capacitance) are calculated based on the design procedure in [10]:

$$L_f = \frac{X_L}{2\pi f_1} = \frac{0.196}{2\pi 50} = 226.19\,\mu H \tag{21}$$

$$C_f = \frac{1}{2\pi f_1} \cdot \frac{1}{X_C} = 39\,\mu F \tag{22}$$

Table 9. Output Filter Design. Technical specifications and results

| Output filter design  Output filter design                                                                                                                        |                                             |                  |                    |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------|--------------------|--|--|

| 1) The load of the inverter is assumed nonlinear. 2) The output filter is lossless and the third harmonic current is 70% of the fundamental 3) THD requirement=3% |                                             |                  |                    |  |  |

|                                                                                                                                                                   | THD*                                        | XL/XC            | 0.03               |  |  |

|                                                                                                                                                                   | third harmonic,                             | h                | 3.00               |  |  |

|                                                                                                                                                                   | The voltage ratio:                          | V3/V1            | 0.03               |  |  |

| Input data                                                                                                                                                        | The third harmonic current component        | I3[A]            | 30.98              |  |  |

|                                                                                                                                                                   | The fundamental output voltage              | V1[V]            | 220.00             |  |  |

|                                                                                                                                                                   | The frequencies ratio:                      | n=fs/f1          | 200.00             |  |  |

|                                                                                                                                                                   | Design relationship                         | XL/XC>=34.33/n^2 |                    |  |  |

|                                                                                                                                                                   | Inductor impedance                          | XL[ohm]          | 0.07               |  |  |

|                                                                                                                                                                   | Minimum Capacitor impedance                 | XCmin[ohm]       | 2.37               |  |  |

|                                                                                                                                                                   | Maximum Capacitor impedance                 | XCmax[ohm]       | 82.75              |  |  |

|                                                                                                                                                                   | The filter inductance                       | L[uH]            | 226.19             |  |  |

| Output data                                                                                                                                                       | The maximum value of the filter's           |                  |                    |  |  |

|                                                                                                                                                                   | capacitor                                   | Cmax[uF]         | 1345.22            |  |  |

|                                                                                                                                                                   | The minimum value of the filter's capacitor | Cmin[uF]         | 38.49              |  |  |

|                                                                                                                                                                   | The final value for the filter capacitor    | C[uF]            | 39.00              |  |  |

|                                                                                                                                                                   | The filter resonant frequency               | fr[Hz]=          | 1695.41            |  |  |

|                                                                                                                                                                   |                                             | (fr/f1)max=      | 34.13              |  |  |

|                                                                                                                                                                   | Check point                                 | fr/f1=           | <mark>33.91</mark> |  |  |

Based on these designed values, inductors with  $230\mu H$  and capacitor with  $50\mu F$  were selected from a manufacture.

## 5. CONCLUSIONS

This paper has discussed the design methodology for the fuel cell inverter system. The topology for this design has been resulted from the specific objectives of the stand-alone fuel cell power system. For this project the 220Vac, 50Hz single phase stand-alone inverter has been used. The model parameters are derived through the design process by using the developed Microsoft Excel tool, described also in the first and second part of the paper. The identification and validation of the major fuel cell power system component models are evaluated according to the measured data of the components and from the manufacturer's data sheet. The operational performance of the system is not only depending on the component efficiency but also on the system design and consumption behavior. All the data have been used in a Matlab/Simulink resulting in a fuel cell power system simulator.

Due to the limited length of paper the author has not introduced the Matlab/Simulink simulator used for analysis of the fuel cell power system efficiency. The simulator has been developed in order to make possible the rapid system prototyping using the dedicated digital signal processors boards, like dSPACE.

## **REFERENCES**

- [1] Shireen, W.; Arefeen, M.S., An utility interactive power electronics interface for alternate/renewable energy systems, Energy Conversion, IEEE Transactions on, Volume: 11 Issue: 3, Sept. 1996 Page(s): 643 –649

- [2] Lai, J-S, A High-Efficiency Low-Cost DC-DC Converter for SOFC. Performance and Control of V6 Converter, SECA Core Technology Program Review Meeting, Boston, Massachusetts, Virginia Polytechnic Institute and State University, Future Energy Electronics Center, May 11 May 13, 2004

- [3] Gaiceanu,M., Sizing of a Stand-Alone PEM Fuel Cell Power System, Part II: The Battery Pack and Half-Bridge Power Converter Design, The National Conference on Industrial Energetic with International Participatio, The 6<sup>th</sup> Edition, Bacau, 2007 (under publishing)

- [4] Jiang, H.J., Qin, Y., Du, S.S., Yu, Z.Y., Choudhury, S., *DSP based Implementation of a Digitally-Controlled Single Phase PWM Inverter for UPS*, Telecommunications Energy Conference, 1998,INTELEC. Twentieth International, 1999, Page(s): 221 -224

- [5] Abdel-Rahim, N., Quaicoe, J.E. Multiple feedback loop control strategy for single-phase voltage source UPS inverter, Power Electronics Specialists Conference, PESC '94 Record., 25th Annual IEEE ,1994, Page(s): 958-964 vol.2

- [6] Shih-Liang Jung, Hsiang-Sung Huang, Meng-Yueh Chang, Ying-Yu Tzou, *DSP-based Muliple-Loop Control Strategy for Single-Phase Inverters Used in AC Power Sources*, Power Electronics Specialists Conference, 1997. PESC '97 Record., 28th Annual IEEE Volume: 1, 1997, Page(s): 706-712 vol.1

- [7] Abdel-Rahim, N.M., Quaicoe, J.E. Analysis and Design of a Multiple Feedback Loop Control Strategy for Single-Phase Voltage-Source UPS Inverters, Power Electronics, IEEE Transactions on Volume: 11 4, July 1996, Page(s): 532-541

- [8] Robert W. Erickson, Dragon Maksimovic, Fundamentals of Power Electronics, Kluwer Academic Publishers, 2001

- [9] Mazumdar, J., Batarseh, I., Kutkut, N., Demirci, O., *High frequency low cost DC-AC inverter design with fuel cell source for home applications*, IAS 2002, Vol.2, Page(s) 789-794

- [10] R. Gopinath, D. Kim, J. H. Hahn, M. Webster, J. Burghardt, S. Campbell, D. Becker, P. N. Enjeti, M. Yeary, J. Howze, *Development of a Low Cost Fuel Cell Inverter System with DSP Control*, IEEE PESC 2002 Conf. Rec., June 2002, vol. 1, pp. 309-314

## **ACKNOWLEDGEMENTS**

The work described in the paper has been performed at Politecnico di Torino- Italy under the Research Fellowship Contract No. 4256.VI.14/20032006, the author being solely responsible for the information provided. With this respect, the author thanks to the 5E research Group of the Politecnico di Torino.